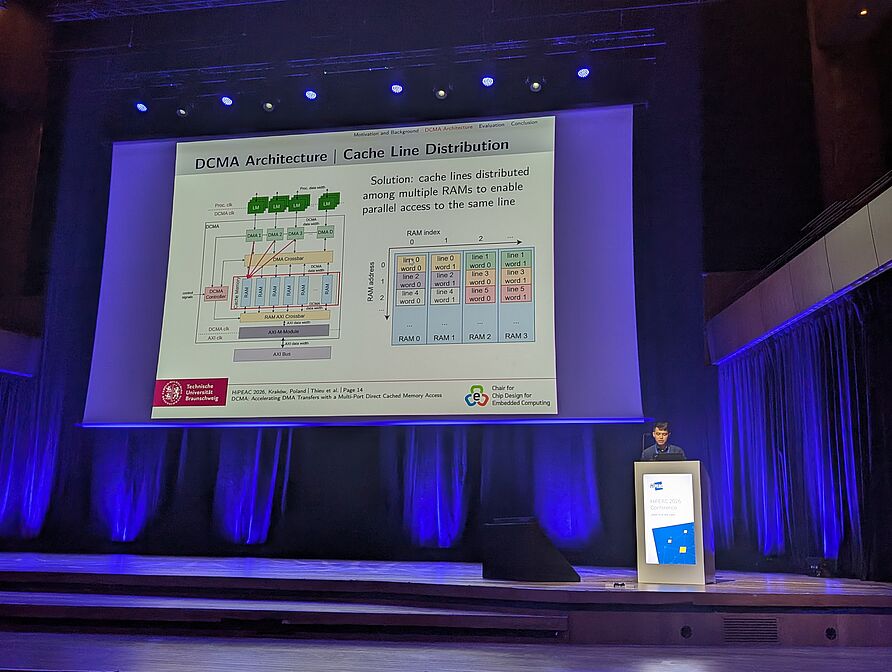

Auf der HiPEAC 2026 vom 26.–28. Januar in Kraków präsentierte Gia Bao Thieu seinen Journalbeitrag aus dem Jahr 2025 zum Direct Cached Memory Access (DCMA).

Die Arbeit, veröffentlicht in den ACM Transactions on Architecture and Code Optimization (TACO), beschreibt eine neuartige Speicherarchitektur, die klassische DMA-Mechanismen mit Cache-Funktionalität kombiniert, um Speicherengpässe in KI-Beschleunigern zu reduzieren. Evaluierungen auf einem Xilinx UltraScale+ FPGA in Kombination mit dem V2PRO-Vektorprozessor zeigen Leistungssteigerungen von bis zu 17× für das neuronale Netz ResNet-50.