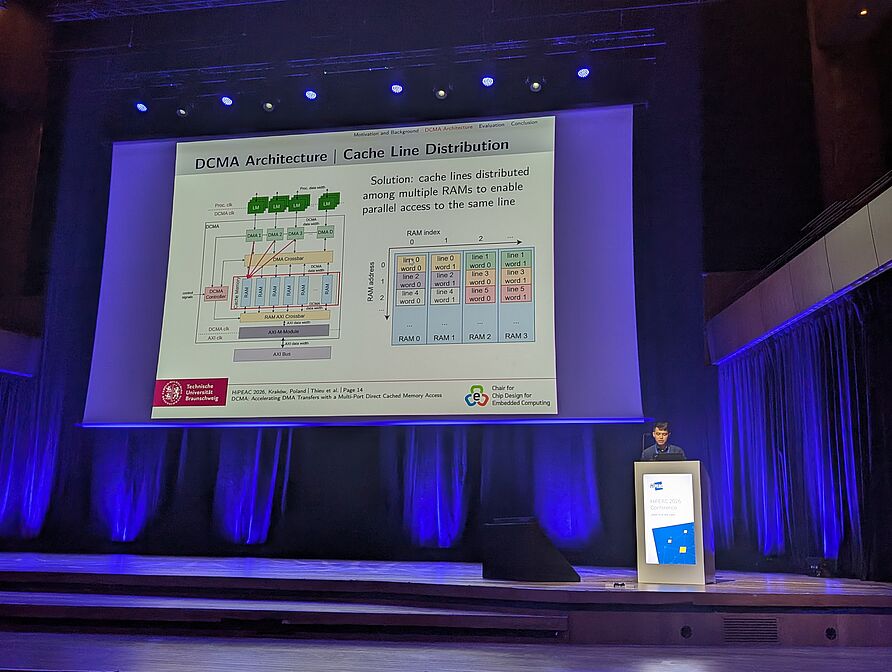

At HiPEAC 2026, held from 26–28 January in Kraków, Gia Bao Thieu presented his 2025 journal paper on the Direct Cached Memory Access (DCMA).

The work, published in ACM Transactions on Architecture and Code Optimization (TACO), introduces a novel memory architecture that combines classical DMA mechanisms with cache functionality to reduce memory bottlenecks in AI accelerators. Evaluations on a Xilinx UltraScale+ FPGA in combination with the V2PRO vector processor demonstrate performance improvements of up to 17× for the ResNet-50 neural network.