# EINSCHALTSTROMPEAKS BEI SIC-JFET IN HALBBRÜCKEN

#### I. Koch

### 1 EINLEITUNG

In leistungselektronischen Anwendungen sollten sich Ober- und Unterschalter einer konventionellen Brückenschaltung nicht gegenseitig beim Schalten beeinflussen, um Kurzschlussströme und somit zusätzliche Verluste oder sogar ein Zerstören der Halbleiter zu vermeiden. Allerdings sind z. B. die optimalen Steuerparameter bei Leistungshalbleiterschaltern auf Basis neuer Halbleitermaterialien oder -strukturen im Entwicklungsstadium oft unidentifiziert, was bei sensiblen Steuereingängen zu einer Beeinflussung der Halbleiter und erheblich erhöhten Schaltverlusten führen kann [1], [2]. Der Fokus dieses Beitrages liegt auf der Beschreibung des Einschaltüberstromes, der bei der Verwendung neuer Schalter auf Basis des Halbleitermaterials Siliziumkarbid (SiC) auftreten und zu erhöhten Verlusten führen kann.

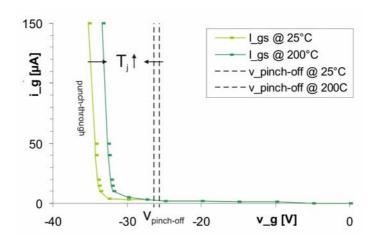

Bei der Spezifizierung der Gate-Spannung  $v_g$  von selbstleitenden JFET muss beachtet werden, dass der zum Ausschalten benötigte Gate-Spannungslevel unterhalb der Pinch-off Spannung liegt, damit der Kanal abgeschnürt wird und der Schalter sperrt. Der Spannungslevel darf jedoch nicht zu niedrig gewählt werden, um einen zu starken Gate-Stromanstieg in der Punchthrough Region zu vermeiden (**Bild 1**).

**Bild 1:** Gate-Strom eines SiC-JFET über der Gate-Spannung mit Pinch-off Spannung und Punch-through Region

Da das sich ergebende Fenster für eine geeignete Sperrspannung von der Junction-Temperatur (T<sub>J</sub>) abhängt, erscheint für ein temperaturunabhängiges Gate-Verhalten ein Ausschaltspannungslevel von -30 V vorerst angemessen. Der Einschaltspannungslevel sollte bei 0 V liegen.

2 Jahresbericht 2009

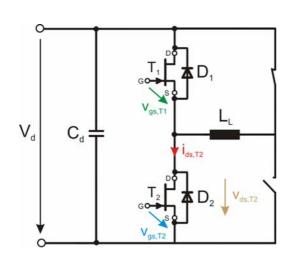

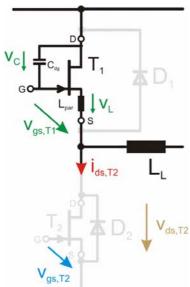

**Bild 2** zeigt den Schaltplan einer Kommutierungszelle mit SiC-JFETs (T1, T2) und SiC-Freilaufdioden (D1, D2) an einer Spannungsquelle, die als typischer Testaufbau für grundlegende Untersuchungen genutzt wird. Zur Untersuchung des dynamischen Verhaltens der Schalter wird T2 geschaltet und T1 kontinuierlich gesperrt.

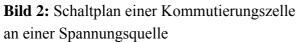

**Bild 3:** Prinzipielle Verläufe von Drain-Source-Spannung, Drain-Strom und Gate-Spannung der JFET in einer Halbbrücke

Die hierzu gehörenden prinzipiellen Verläufe der Drain-Source-Spannung  $v_{ds,T2}$ , des Drain-Stromes  $i_{ds,T2}$  und der Gate-Spannung  $v_{gs,T2}$  des Schalters T2 sowie der Gate-Spannung  $v_{gs,T1}$  des sperrenden Schalters T1 sind in **Bild 3** dargestellt. Beim Einschalten ist manchmal in den gemessenen Stromverläufen eine Stromspitze sichtbar, die zusätzliche Schaltverluste verursacht und im Folgenden näher erläutert werden soll.

## 2 BESTANDTEILE DES STROMÜBERSCHWINGERS

Der beschriebene Einschaltstrompeak besteht aus bis zu vier Anteilen, die je nach Halbleiterbauelementdimensionierung und Randbedingungen unterschiedlich ausgeprägt sind. Ein Anteil entsteht durch die Rückwärtserholeigenschaften der Diode. Maßgeblich hierfür sind die Ladungsträger  $Q_{rr(D)}$ , die bei der Stromkommutierung ausgeräumt werden müssen, damit die Diode und somit das obere Halbleiterpaar, bestehend aus Schalter und Diode, sperrt. Weiter bilden die Sperrschichten der Halbleiterschalter Kapazitäten, deren Ladungen  $(Q_{C(T)})$  ebenfalls zu Überströmen führen können. In Aufbauten mit größeren Abmessungen können auch parasitäre aufbaubedingte Kapazitäten einen Beitrag liefern  $(Q_{C(par)})$ . Da neue Halbleitersamples aber oft nur für kleine Leistungsklassen verfügbar sind und somit sowohl die Sperrschichten als auch die Aufbauabmessungen relativ klein sind, können diese Überstromanteile bei realen Messungen weitestgehend vernachlässigt werden. Bei Einsatz von SiC-Schottky-Dioden ist aufgrund der Unipolarität des Bauelementes keine Speicherladung und damit auch kein entsprechender Beitrag zum Strompeak vorhanden [3].

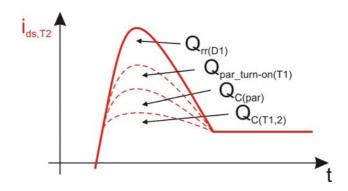

**Bild 4:** Anteile am Einschaltüberstrom bei JFET in Halbbrücken

Gemessene Einschaltstrompeaks werden trotz obiger Argumentation oft nur diesen Anteilen zugeordnet. Jedoch kann bei den vorgestellten SiC-JFET aber auch bei anderen Halbleiterstrukturen wie z.B. dem MOSFET (unabhängig vom Halbleitermaterial) ein ungewolltes Einschalten hervorgerufen werden. Gerade, wenn nicht angemessene Steuerparameter gewählt werden, kann dieses Einschalten einen maßgeblichen Anteil zum Strompeak liefern und damit zu deutlich erhöhten Schaltverlusten führen. In **Bild 4** wird dieser Anteil mit Q<sub>par turn-on(T1)</sub> angedeutet.

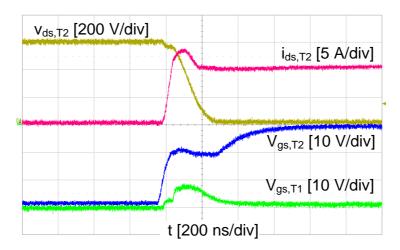

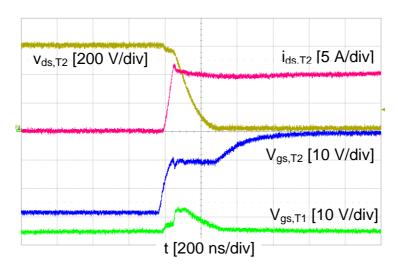

**Bild 5** zeigt gemessene Kurven der Drain-Source Spannung  $v_{ds,T2}$  (olive), des Drain-Stroms  $i_{ds,T2}$  (rot), der Gate-Spannung  $v_{gs,T2}$  des unteren JFET T2 (blau) und der Gate-Spannung  $v_{gs,T1}$  des sperrenden Oberschalters T1 (grün) beim Einschalten eines JFET in einer Halbbrücke. Hierbei ist ein Überstrom im Drain-Strom  $i_{ds,T2}$  gut erkennbar.

**Bild 5:** Typischer Einschaltvorgang eines JFET in einer Halbbrücke mit ungewolltem Einschalten des korrespondierenden Schalters. Die Gate-Spannung des korrespondierenden Schalters liegt bei -30 V ( $R_G = 150 \Omega$ ).

Zeitgleich bricht die Gatespannung  $v_{gs,T1}$  zusammen, was auf das ungewollte Einschalten hindeutet. Unter Berücksichtigung von **Bild 1** wird ersichtlich, dass das Einbrechen auf -22 V oberhalb der Pinch-off-Spannung von ca. -26 V liegt und somit der JFET nicht vollständig sperren kann. Allerdings kann auch kein hoher Kurzschlussstrom entstehen, da der JFET in diesem Bereich noch einen relativ hohen Durchlasswiderstand besitzt.

4 Jahresbericht 2009

Der Einbruch der Gate-Spannung  $v_{gs,T1}$  entsteht durch den Potentialsprung des Halbbrückenmittelpunktes während des Einschaltens von T2. Hierbei rufen die Strom- und die Spannungsflanke Spannungsabfälle an der Induktivität  $L_{par}$  des Source-Pfades im Halbleitermodul T1 und am Drain-Gate-Kondensator  $c_{dg}$  hervor.

V<sub>gs,T2</sub> **Bild 6:** Schaltbild mit den für das ungewollte Einschalten relevanten Komponenten

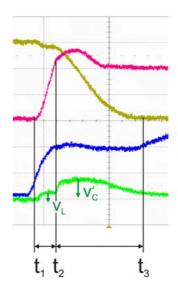

**Bild 7:** Ausschnitt des Einschaltvorgangs aus **Bild 5**

Für die weitere Beschreibung ist in **Bild 6** das Schaltbild mit den relevanten Komponenten dargestellt. **Bild 7** zeigt einen Ausschnitt des Einschaltvorganges mit den Spannungsabfällen an der Kapazität  $v_C$  und an der Induktivität  $v_L$ . Da über dem Kondensator allerdings hauptsächlich die Sperrspannung des Schalters abfällt, wird die Größe  $v_C$  eingeführt, die lediglich den Spannungsabfall durch den Umladestrom berücksichtigt.

Zum Zeitpunkt  $t_1$  ist der Umladevorgang des Gates vom Schalter T2 soweit fortgeschritten, dass  $v_{1gs,T1}$  die Pinch-off-Spannung von -26 V unterschreitet. Hier übernimmt T2 den Strom. Bis  $t_2$  steigt der Strom mit einem nahezu konstanten di/dt an. Dieses führt zum Spannungsabfall  $v_L$  an der parasitären Induktivität  $L_{par}$ . Währenddessen ist die Drain-Source-Spannung von T2 konstant um die Summe aller Spannungsabfälle an den parasitären Induktivitäten des Halbbrückenpfades reduziert. Zwischen  $t_2$  und  $t_3$  sinkt dann die Drain-Source-Spannung mit der Spannungssteilheit du/dt ab und ändert dementsprechend das Potential des Halbbrückenmittelpunktes. Der Halbbrückenmittelpunkt ist allerdings ebenfalls Bezugspunkt für das Gate des Oberschalters T1 und hieran mit der Gate-Kapazität  $c_{dg}$  gekoppelt. Daher kann die Gate-Spannung nicht beliebig schnell dem Potentialsprung folgen und führt im Fall höherer Spannungssteilheiten du/dt zum Spannungseinbruch  $v_C$ . Beide Effekte machen sich in einem zusätzlichen Anteil am Einschaltüberstrom bemerkbar und sind in **Bild 4** als  $Q_{par\_turn-on(T1)}$  zusammengefasst.

Dieser Effekt kann beeinflusst werden, indem ein zusätzliche Kondensator zwischen Gate und Source geschaltet und somit  $v_{gs,T1}$  geglättet wird. Allerdings kann hiermit der

Stromüberschwinger nicht vollständig verhindert werden, da die Kapazitäten aufgrund der gewünschten hohen Schaltgeschwindigkeiten nur klein sein dürfen. Ein weiterer Parameter ist der Gate-Widerstand, der bei Reduzierung zwar zu einem höheren Umladestrom der Source-Gate-Kapazität führt, aber gleichzeitig auch steilere Flanken verursacht, die wiederum zu einem höheren Spannungseinbruch führen. In Tests konnte gezeigt werden, dass sich beide Effekte annähernd kompensieren und im Ergebnis die gleiche Amplitude des Stromüberschwingers resultiert.

## 3 ANPASSUNG DES GATE-SPANNUNGSLEVELS

Um den Strompeak zu reduzieren, ist eine Anpassung der Gate-Spannung zweckmäßiger. Hierfür sollte der Gate-Spannungslevel soweit abgesenkt werden, dass trotz des Spannungseinbruches  $V_{pinch-off}$  nicht überschritten wird. Allerdings muss weiterhin der in **Bild 1** erkennbare Gate-Stromanstieg im Punch-through-Bereich im zulässigen Bereich bleiben. Die Messkurven für einen Einschaltvorgang bei einer Gate-Spannung von -35 V sind in **Bild 8** dargestellt. Hierbei ist ersichtlich, dass ein Gate-Spannungseinbruch zwar weiterhin vorhanden ist, aber nicht mehr zum Einschalten des Schalters führt.

**Bild 8:** JFET-Einschaltcharakteristik in einer Halbbrücke ohne ungewolltes Einschalten des Oberschalters bei einem Sperrspannungslevel von -35 V des sperrenden Schalters ( $R_G = 150 \Omega$ )

Als Resultat ist im Stromverlauf der Überstrom auf das Minimum reduziert. Der restliche Überschwinger ist in einer Größenordnung, die den genannten parasitären kapazitiven Ladungen des JFET-Dioden-Paares zugeordnet werden kann.

Allerdings bleibt anzumerken, dass in Hinblick auf die starke Temperaturabhängigkeit des Gate-Stromes die Wahl des Sperrspannungslevels von -35 V für höhere Temperaturen kritisch werden könnte und dass der optimale Spannungslevel stark mit der Streuung der Bauteilparameter variieren kann. Daher sollte der gewählte Gate-Spannungslevel nicht zu weit in die Punch-through Region reichen und über den gesamten Temperaturbereich zu

Jahresbericht 2009

zulässigen Gate-Strömen führen. Damit wird der Störabstand des Gates erhöht und das ungewollte Einschalten zumindest reduziert.

Sollte nach der Gate-Spannungsanpassung der Störabstand nicht ausreichen und somit weiter ein ungewolltes Einschalten stattfinden, muss das parasitäre Einschalten durch eine zusätzliche Beschaltung am Gate unterdrückt werden. In Untersuchungen konnte das gleiche Ergebnis wie in **Bild 8** erreicht werden, indem ein Bipolartransistor zum kurzzeitigen Kurzschließen des Gate-Widerstandes eingesetzt wurde. Der Transistor ist während des Schaltvorgangs des korrespondierenden einschaltenden Schalters durchgeschaltet und ermöglicht dadurch hohe Ströme zum Umladen der Drain-Gate-Kapazität und gewährleistet ein sicheres Sperren.

## 4 ZUSAMMENFASSUNG

Der Beitrag beschreibt das ungewollte Einschalten von Halbleitern am Beispiel des SiC-JFET in Halbbrücken. Beim Einsatz von Halbleitern mit sensiblen Steuereingängen können während des Schaltens erhöhte Einschaltüberströme entstehen, die zu erhöhten Schaltverlusten führen. Durch Anpassung der Gate-Spannung kann dieser Effekt weitestgehend verhindert und zusätzliche Verluste reduziert werden.

## LITERATUR

- [1] I. Koch, W.-R. Canders: *Comparison of SiC-JFET and Si-IGBT inverter losses*, ECSCRM 2008, Barcelona, Spain

- [2] B. Allebrand, H.-P. Nee: Comparison of commutation transients of inverters with silicon carbide JFETs with and without body diodes,

NORPIE 2004, Trondheim, Norway

- [3] J. Lutz: *Halbleiter-Leistungsbauelemente*, Springer-Verlag, Berlin Heidelberg 2006